C. Baltay March 19, 2005

# Monolithic CMOS Pixel Detectors for ILC Vertex Detection

¢. Baltay, W. Emmet, H. Neal, D. Rabinowitz Yale University

Jim Brau, O. Igonkina, N. Sinev, D. Strom University of Oregon

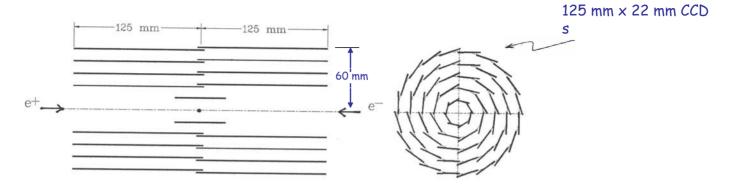

#### ILC Vertex Detector Design

#### Monolithic CMOS Pixel Detectors

Total number of chips 120

| Layer | Radius | Total<br>Length | No of<br>Chips | Chip Size |  |  |  |  |  |

|-------|--------|-----------------|----------------|-----------|--|--|--|--|--|

|       | Cm     | Cm              |                | Cm        |  |  |  |  |  |

| 1     | 1.2    | 5.0             | 8×1            | 5.0×1.2   |  |  |  |  |  |

| 2     | 2.4    | 25.0            | 8×2            | 12.5×2.2  |  |  |  |  |  |

| 3     | 3.6    | 25.0            | 12×2           | 12.5×2.2  |  |  |  |  |  |

| 4     | 4.8    | 25.0            | 16×2           | 12.5×2.2  |  |  |  |  |  |

| 5     | 6.0    | 25.0            | 20×2           | 12.5×2.2  |  |  |  |  |  |

Total Number of Pixels  $1.25 \times 10^{10}$

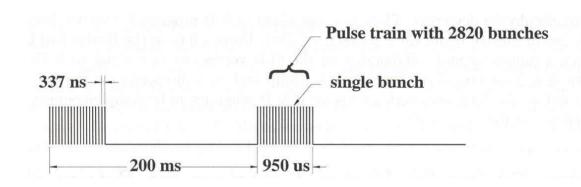

## Time Structure for the TESLA Design

#### Background Calculation:

At 1.5 cm from Interaction Point with 3 Tesla field expect 0.03 hits /mm²/bunch crossing

Will use this number for the entire detector

## Conventional CCD's Not Well Suited for This Application

- Consider SLD type CCD's with  $20\mu \times 20\mu$  pixels 22 mm x 125 mm = 2750 mm<sup>2</sup> with 6.9 x 10<sup>6</sup> pixels/CCD

- Readout time at 25 MHz is 275 msec

May be can push to 50 MHz readout or divide CCD into several readout sections

- → Can readout in 200 msec between pulse trains

- Occupancy, integrating over 2820 bunches in a pulse train

0.03 hits/mm²/bunch x 2820 bunches x 3 pixels/hit

= 250 pixels hit/mm²

or 10% of the pixels have a hit (occupancy)

- SLD Experience occupancy of 10<sup>-3</sup> or 2.5 hits/mm<sup>2</sup> are maximum we could handle!

- → Occupancy too high by factor of ~ 100!!

#### Monolithic CMOS Pixel Detectors

## → What are they?

- New CMOS technology makes pixels as small as  $5 \mu \times 5 \mu$  possible

- Each pixel has its own intelligence (electronics) under the pixel

- Unlike CCD's, all pixels are NOT read out in a raster scan

- Reads out x,y coordinates only of pixels with hit (i.e., exceeding an adjustable threshold) at 25 MHz

- Monolithic design photosensitive detector pixel array and read out electronics for each pixel on the same piece of silicon can be quite thin (few  $\times$  100  $\mu$ ?)

## → Advantages over CCD's

- Significantly faster read out. Typical occupancy of vertex detector at e<sup>+</sup>e<sup>-</sup> collider ~ 10<sup>-3</sup>

1000 times faster read out! (Read only hit pixels!)

- Potentially more radiation hard

- Small 5  $\mu$  x 5  $\mu$  pixels allow good resolution

## → Advantages over hybrid pixel devices used at the LHC

- Monolithic can be much thinner than hybrid devices

- Do not need bump bonding of pixel detector to electronics layer

- Allows much smaller pixels

### First Readout Scheme Considered:

- Bunches within a train separated by 337 nano sec!

- Expected background

~ 0.03 hits/mm²/bunch

- Can NOT integrate over 2820 bunches occupancy too high!

- Plan to read out each bunch in 337 n sec!

- Divide each 22 mm  $\times$  125 mm device into 25 regions (22 mm  $\times$  5 mm = 110 mm<sup>2</sup> each) with a read out for each region

- Expect .03 hits/mm<sup>2</sup>/bunch  $\times$  110 mm<sup>2</sup> ~ 3 hits per bunch in each read out region

- At 25 MHz, can read out average of 3 hits/bunch in 120 n sec, comfortably below the 337 n sec bunch spacing. This allows room for fluctuations in the number of hits/bunch

- There can be buffering in each pixel read out circuit so that larger fluctuations can be tolerated as long as the average rate can be handled.

Problem - Electromagnetic Interference maybe too high for readout during Pulse train!

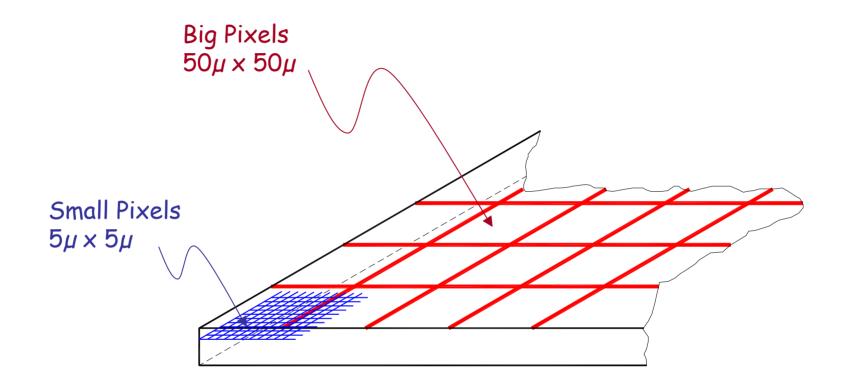

## Present Conceptual Design

- During the past year, working with SARNOFF we developed a conceptual design that:

- we believe will work for an ILC Vertex Detector

- that SARNOFF believes they can build.

- Plan to integrate over pulse train and readout during 200 msec between trains to avoid EMI (Electromagnetic Interference) during train.

- Occupancy would be too high

- BUT for each hit, readout x,y, intensity, AND time of hit (time to better than 300 nsec precision effectively tagging each hit with its bunch crossing number)

- In analyzing Vertex detector data look only at hits which occurred in the same single bunch crossing

- → Occupancy ~ 10<sup>-6</sup> or 0.03 hits/mm<sup>2</sup>!!

## Present Conceptual Design (Continued)

- Accomplish this with a Hierarchical Design Approach.

Each device will have two separate sensitive pixel arrays with its own electronic logic under each pixel

- Big Pixel (Macro Pixel or High Speed) Array

- $50\mu \times 50\mu$  pixels

- Triggers on hits above threshold

- Records time of hit

- Small Pixels (Micro Pixel or High Resolution) Array

- 5μ x 5 μ Pixels

- Addressable, random access array

- Records intensity of hit (3 digit resolution)

## Monolithic CMOS Pixel Detectors

Two active particle sensitive layers:

```

Big Pixels - High Speed Array - Hit trigger, time of hit Small Pixels - High Resolution Array - Precise x,y position, intensity

```

## Array Designs

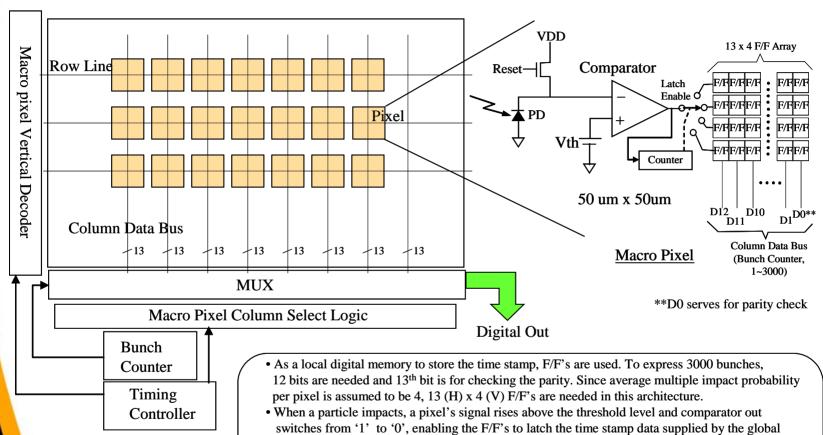

#### **High-speed arrays**

- Designed for quick response.

- Threshold detection only.

- Large pixels ( $\sim$ 50 x 50  $\mu$ m).

- Transmits X,Y location and time stamp of impact.

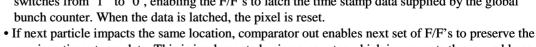

#### **High-resolution arrays**

- Designed for resolution and querying.

- Smaller pixel size ( $\sim$ 5 x 5  $\mu$ m).

- Random access addressability.

- Records intensity.

- Provides intensity information only for pixel region queried.

## Hierarchical Array Operation

- Particles from any particular bunch crossing traverse both the Big and the Small pixel arrays

- The Big Pixels which are hit store the time information (i.e. bunch number) in a 13 bit digital memory located under the area of the Big Pixel. The hit number counter is advanced after each hit. Up to 4 hit times can be stored under each pixel

(The probability of a Big Pixel being hit more than 4 times in a pulse train is  $\leq 10^{-3}$ )

The Small Pixels which are hit store the analog signal charge locally in the area under each pixel for the duration of a pulse train

(Probability of two hits in the same Small Pixel in a pulse train is  $\leq 1\%$ )

## Hierarchical Array Operation (continued)

- Readout starts in the 200 msec gap after each train

- x,y coordinates and intensity from Small Pixels that are hit, with time stamp from the corresponding Big Pixel

- A small fraction of the hits will have ambiguity in time, i.e., more than one time stamp

(This will increase the occupancy by 30% above 10-6)

- Both the Big Pixel and the Small Pixel arrays will be reset before the next pulse train

## Macro Pixel Array Architecture

- If next particle impacts the same location, comparator out enables next set of F/F's to preserve the previous time stamp data. This is implemented using a counter which increments the row address of the F/F array.

- Time stamp information is read out in the random access mode from the pixels of interest which stored nonzero time stamp data.

## Micro Pixel Array Architecture

## Expected Occupancy and Hit Rates

- Estimate for a typical 22 mm  $\times$  125 mm chip using 0.03 hits/mm²/bunch crossing (this is conservative for the outer layers). Assume that each hit will put charge above threshold into, on the average, 3 Small Pixels.

- Each chip will have

```

22 mm x 125 mm = 2750 mm<sup>2</sup>

1.1 \times 10^6 Big Pixels

1.1 \times 10^8 Small Pixels

```

- Integrating over 2820 bunches in a pulse train we expect

- 0.03 hits/mm²/bunch x 2820 bunches ≈ 85 hits/mm²

- ~ 20% probability of a hit in a Big Pixel

(~ 4% probability of 2 hits, 0.8% 3 hits, 0.16% 4 hits)

- $6 \times 10^{-3}$  occupancy in Small Pixels per pulse train  $2 \times 10^{-6}$  occupancy in Small Pixels per bunch crossing

- Effective Occupancy ~ 2 x 10<sup>-6</sup>!!

- Total number of hits per 22 mm  $\times$  125 mm chip  $7 \times 10^5$  Small Pixel hits/pulse train

- Readout time 7 x 10<sup>5</sup> hits/25 MHz ~ 28 msec + some overhead

#### Other Comments & Issues

#### Thickness

Present state of the art is 100 to 200  $\mu$  total thickness for the sum of the Macro and Micro Arrays. Could improve with some R&D to maybe 50  $\mu$ .

#### 2. Power Consumption

Present estimate 1.8 watts/chip could improve with R&D.

- 3. Fabrication Issues two possible approaches

- a) Both Macro and Micro Pixel Arrays fabbed in a single process on the same piece of silicon.

- b) Macro and Micro Pixel Arrays fabbed in separate processes, then bonded together. No electrical connections needed between Macro and Micro Pixels in active area of detector all connections are at one end of the chip.

#### 4. Stitching

Present layout tooling allow 21 mm  $\times$  21 mm devices - will have to learn how to "stitch" these areas together to make our size devices. They don't think this is a problem but they have not actually done it yet in CMOS process.

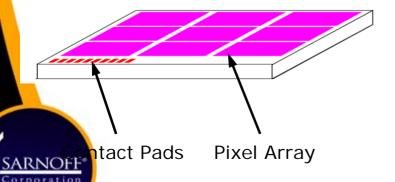

#### 5. First Prototype

- a) The first prototypes will probably be 5 mm  $\times$  5 mm devices with the readout logic on a separate chip.

- b) In the final 22 mm  $\times$  125 mm active area device the readout logic can be on the same chip, at one end, making the actual device 22 mm  $\times$  130 mm long. Output connections will be at one end (away from interaction point).

## Statement of work

Task-1: Design and layout the micropixel (Sarnoff)

Task-2: Design and layout the macropixel (Sarnoff)

Task-3: Fabricate the test chips using MOSIS shuttle (Sarnoff)

Task-4: Particle bombardment on test chip (Yale/Oregon)

Task-5: Perform testing on test chip (Yale/Oregon w/ consulting from Sarnoff)

Task-6: Summarize data (Yale/Oregon/Sarnoff)

Task-7: Write report (Yale/Oregon/Sarnoff)

## Program Plan

|    |           |                                    | Q1 |    | Q2 |    | Q3 |    |    | Q4   |    |     | Q5  |     |     | Q6  |     |     | Q7       |     |     |

|----|-----------|------------------------------------|----|----|----|----|----|----|----|------|----|-----|-----|-----|-----|-----|-----|-----|----------|-----|-----|

| ID | 0         | Task Name                          | M1 | M2 | M3 | M4 | M5 | M6 | M7 | M8 I | M9 | M10 | M11 | M12 | M13 | M14 | M15 | M16 | M17      | M18 | M19 |

| 1  | <b>II</b> | Micropixel design and layout       |    |    |    |    |    |    | h  |      |    |     |     |     |     |     |     |     |          |     |     |

| 2  | <b>=</b>  | Macropixel design and layout       |    |    |    |    |    |    | L  |      |    |     |     |     |     |     |     |     |          |     |     |

| 3  |           | MOSIS test run                     |    |    |    |    |    |    |    |      |    |     |     |     |     |     |     |     |          |     |     |

| 4  |           | Particle bombardment on test chips |    |    |    |    |    |    |    |      | Ĭ  |     |     |     |     |     |     |     |          |     |     |

| 5  |           | Testing of chips                   |    |    |    |    |    |    |    |      |    |     |     |     |     |     |     |     | <b>1</b> |     |     |

| 6  |           | Summarize test date                |    |    |    |    |    |    |    |      |    |     |     |     |     |     |     |     |          | h ' |     |

| 7  |           | Write report                       |    |    |    |    |    |    |    |      |    |     |     |     |     |     |     |     |          |     |     |

## **Estimated ROM Cost**

The estimated ROM for this phase is: \$260,000